FLIP FLOP (TEKNIK DIGITAL + PRAKTEK)

MATERI FLIP-FLOP

Flip-flop merupakan salah satu pengaplikasian dari beberapa gerbang digital sehingga dapat menyimpan bilangan biner 1 bit. Pada dasarnya rangkaian Flip-flop terdiri dari sebuah rangkaian multivibrator bistabil. Rangkaian Flip-flop juga merupakan dasar dari rangkaian memori yang sudah kita kenal sekarang. Karena rangkaian Flip-flop pada teknik digital memiliki sifat kondisi output yang tidak hanya bergantung pada kondisi input, akan tetapi bergantung juga pada kondisi input sebelumnya.

Flip-flop memiliki dua keluaran yang dinamakan sebagai kondisi Q dan Q’, yang mana Q’ adalah kondisi kebalikan dari Q. Rangkaian Flip-flop sudah ditemukan sejak tahun 1918 oleh seorang ahli fisika dari Inggris. Saat itulah dikembangkan rangkaian-rangkaian penyimpan data hingga saat ini. Bisa dikatakan Flip-flop merupakan rangkaian memori 1 bit dengan keluaran 1 atau 0 saja. Saat ini dikenal beberapa jenis rangkaian Flip-flop, yaitu SR Flip-flop, JK Flip-flop, D Flip-flop, dan T Flip-flop.

🔗 SR Flip-Flop

SR Flip-flop meruapakan jenis flip-flop yang paling sederhana. Disebut sebagai SR karena flip-flop ini memiliki masukan Set dan Reset maka disebut dengan SR Flip-flop. SR Flip-flop terdiri dari satu rangkaian bistabil dan hanya dapat mengoperasikan satu bit bilangan biner. Ada berbagai jenis konfigurasi yang dapat dibuat dalam membangun sebuat SR Flip-flop, diantaranya adalah dengan menggunakan dua buah gerbang NAND, atau dengan dua buah gerbang NOR. Kedua masing-masing gerabang (NAND atau NOR) dihubungkan saling menyilang, yakni output salah satu gerbang NAND dihubungkan ke bagian input gerbang NAND lainnya. Begitu juga halnya dengan gerbang NOR.

Adapun tabel kebenaran dari SR flip-flop adalah sebagai berikut:

| S | R | Q |

| 0 | 0 | Kedaan terakhir |

| 1 | 0 | 1 (set) |

| 0 | 1 | 0 (reset) |

| 1 | 1 | tak terdefinisi |

Seperti pada penjelasan sebelumnya, Flip-flop SR dapat dibangun dengan menggunanaan dua buah gerbang NOR maupun gerbang NAND.

* Prinsip kerja SR Flip-flop dengan gerbang NOR

Rangkaian diatas dibangun dengan 2 buah nor gate yang akan menghasilkan nilai output 1 pada Q jika salah satu inputnya berlogika 1. Misalnya, apabila input R diberikan kondisi logika 1 dan S=0, maka output Q akan menghasilkan logika 1. Karena output gerbang NOR pertama dihubungkan dengan input gerbang NOR yang kedua, maka pada saat output Q bernilai 1 maka output Q’ akan berkondisi sebaliknya.

Sekarang ketika input input R diberikan logika 0 dan S=1, maka output Q akan berubah menjadi 0 dan Q’=1. Namun jika R dan S sama-sama berlogika 0, maka output Q akan tertahan pada kondisi sebelumnya sampai kondisi input berubah kembali. maka dari itulah flip-flop disebut juga dengan memori 1 bit karena dapat menyimpan kondisi tadi.

* Prinsip kerja SR Flip-flop dengan gerbang NAND

Sedikit berbeda dengan SR flip-flop dengan gerbang NOR, rangkaian flip-flop dengan gerbang NAND, output Q dan Q’ akan sama-sama berlogika 1 jika input S dan R berlogika 0. Hal ini berupakan kebalikan dari tabel kebenaran SR flip-flop yang menggunakan gerbang NOR. Namun pada flip-flop pada kondisi ini haruslah dihindari, itulah sebabnyak dalam tabel kebenaran tertulis tidak terdefinisi.

Pada flip-flop gerbang NAND, apabila kondisi S=1 dan R=0, maka output Q akan berlogika 1, yang mana output dari Q ini akan masuk juga ke bagian input gerbang NAND yang kedua, sehingga output gerbang NAND yang kedua akan menjadi 0, dan sebaliknya. Pada saat input S=0 dan R=1, maka kondisi output Q akan menjadi berubah menjadi 1. Namun apabila S dan R diubah menjadi sama-sams berlogika 1, maka output Q akan mengikuti kondisi sebelumnya. Berikut tabel kebenaran dari SR flip-flop dengan gerbang NAND.

🔗 JK Flip-Flop

Jk flip-flop merupakan jenis flip-flop yang dibangun dengan dua buah SR flip-flop clocked yang digabungkan menjadi satu. Yang mana kedua output dari flip-flop yang pertama dihubungkan dengan input flip-flop kedua secara berderet. Sedangkan output flip-flop yang kedua diumpanbalikan kepada input flip-flop yang pertama sehingga flip-flop yang pertama dapat disebut sebagai master (induk), dan flip-flop kedua disebut sebagai slave (pembantu). Sifat flip-flop yang kedua akan mengikuti sifat flip-flop yang pertama.

Dari gambar diatas dapat dijelaskan bahwa flip-flip yang pertama dapat bekerja apabila diberikan pulsa clock 1, sedangkan flip-flop yang kedua akan bekerja pada pulsa clock 0. Hal ini karena adanya gerbang NOT (inverter) dari input clock flip-flop yang pertama ke input flip-flop yang kedua.

Ketika input clock diberikan pulsa 1, maka flip-flop master akan meneruskan informasi yang diberikan dari input J-K, namun flip-flop slave belum bekerja. Namun ketika pulsa clock berubah menjadi 0, maka flip-flop master yang akan berhenti bekerja dan bagian slave-lah yang akan meneruskan informasi dan bekerja sebagai master.

Dari gambar diatas juga terlihat bahwa pada flip-flop yang pertama terdapat input set dan reset. Hal ini berfungsi untuk menset Q menjadi berlogika 1 tanpa terpengaruh oleh input J-K. Sedangkan input clock Cp berfungsi sebagai pengontrol set ketika dalam keadaan 0.

Pada saat input J=0 dan K=1, maka output Q akan berlogika 0 atau reset, itupun ketika pulsa pertama masuk ke input Cp yang bergerak dari 1 ke 0. Kemudian ketika input J=1 dan K=1, maka output Q akan berubah setiap pulsa clock Cp masuk dan bergerak dari 1 ke 0. Perubaahan seperti ini disebut juga dengan toggle.

Berikut ini adalah tabel kebenaran dari J-K flip-flop :

| J | K | Qn+1 | Keterangan |

| 0 | 0 | Qn | kondisi menyimpan |

| 0 | 1 | 0 | kondisi reset |

| 1 | 0 | 1 | kondisi set |

| 1 | 1 | 0 | kondisi toggle |

🔗 D Flip-Flop

D Flip-flop merupakan salah satu rangkaian flip-flop yang populer dan banyak dipakai dalam rangkaian dasar memori. Karena fungsi D flip-flop yang real dapat menyimpan data 1 bit untuk sementara waktu. Waktu ini lah sering disebut dengan delay flip-flop atau D-Latch.

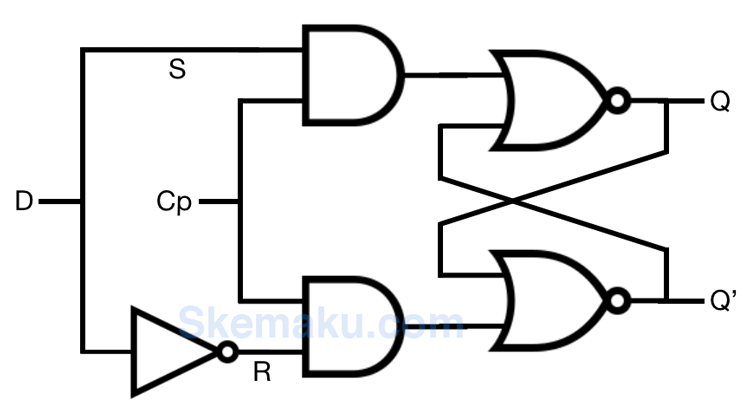

Pada dasarnya D Flip-flop ini hampir sama dengan SR Flip-flop dengan clock, hanya saja yang membedakannya adalah input S dan R dijadikan input D yang ditambahkan gerbang NOT (inverter).

Dari gambar diatas terlihat bahwa rangkaian flip-flop D tersusun atas SR flip-flop yang sedikit dimodifikasi dengan tambahan gerbang NOT (inverter) yang menghasilkan input baru D. Informasi data yang berada pada masukan D akan disimpan pada output Q hanya apabila input clock Cp dalam keadaan 1 pulsa. namun jika clock Cp berkondisi 0, maka perubahan informasi pada input D tidak akan mempengaruhi output Q sampai kondisi Cp 1 kembali.

🔗 T Flip-Flop

T Flip-flip merupakan salah satu jenis flip-flop yang kedua outputnya diumpan balikan kembali (feedback) ke bagian input SR flip-flop. Adapun rangkaiannya T flip-flop adalah sebagai berikut :

Dari gambar dibawah dapat dijelaskan prinsip kerjanya bahwa ketika input T diberikan logika 0, sedangkan S dan R juga berkondisi logika 0, maka output Q akan menghasilkan logika 0 juga, untuk Q’ tentu akan berkondisi kebalikan dari Q, yakni 1. Ketika flip-flop dalam kondisi tersebut, maka input di bagian satu gerbang NAND memiliki logika 1 (set).

Ketika T diubah menjadi 1 dan S1, maka output Q yang sebelumnya berkondisi 0 akan berubah menjadi 1. Nah dari gambar terlihat bahwa output Q terhubung ke dalam input gerbang NAND yang kedua. Namun karena clock T berkondisi 1 hanya beberapa saat dan kembali menjadi 0, maka kondisi logika R akan 0 dan S tetap 1.

Pada kondisi tersebut, input R menjadi berlogika 1, artinya siap reset. Artinya output Q yang sebelumnya 1 akan berubah ke kondisi 0 jika input T mendapatkan pulsa 1 kembali. dan seterusnya, dan seterusnya sehingga output Q akan selalu berubah apabila input T mendapatkan pulsa 1.

Komentar

Posting Komentar